Skylake架构解析 指令执行前端明显提升

这代skylake最明显提升的是指令执行前端(处理器架构分两部分,一部分是指令执行前端,一部分是后面的运算单元部分,前者决定了处理器运算的效率,后者则是运算的能力!),提升包括更高分支预测效率,更大的微指令缓存,更快的指令预取速度,更高度并行化的乱序执行技术,剩下就是AES相关的提升了。(此部分文件翻译自Techbang,小编有对内容进行个人理解下的润色)

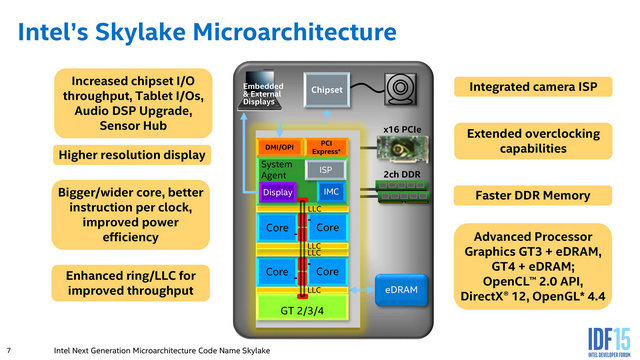

上面这张图片展示出 Skylake 的改进之处,除了已知的新品组 I/O 部分有重大改变之外,核心部分没有意外地朝向每个时脉更多指令、提升效率的方向进行。负责连结核心内部各处功能的 Ring 和 LLC 部分,也提升了吞吐量性能,镜头捕捉影像后负责处理的 ISP 也内建在核心之中。

其它部分就是已知的规格,内存部分升级 DDR4 双通道,全面支持 DirectX 12、部分产品会采用 GT3+eDRAM 以及 GT4+eDRAM 的封装形式。超频能力因为 BCLK 基本参考外频独立,而能够大幅超频不影响其它 PCIe 的运作。

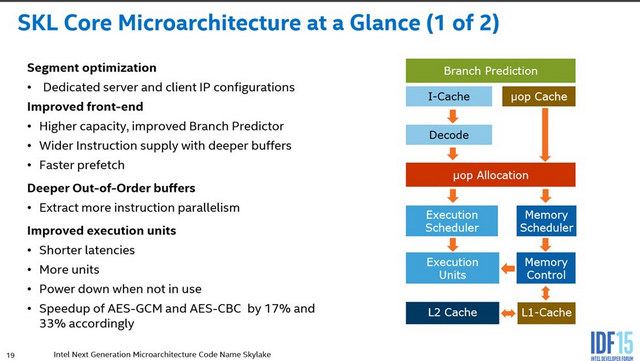

接下来的简报中,可以看见 Skylake 强化了前端部分,分支预测器的容量和准确度皆有提升,更大的缓冲区提供更更多的指令特性,以及更快的预取速度。乱序执行缓冲区也提升容量,能够提取更多指令加强平行化处理。

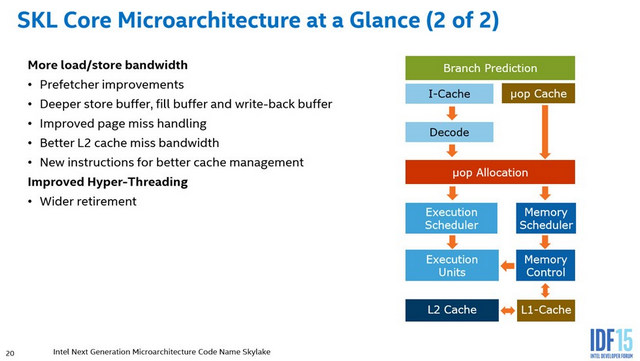

处理单元部分加入更多的单元,同时减少处理延迟,当单元不处理时就关闭省电,AES-GCM 和 AES-CBC 加密演算法可分别提升 17% 和 33%。载入与储存频宽也因为缓冲区的加大随着变大,也换了更好的演算法处理 page miss 和 L2 读取问题,将执行结果回写和移除指令的单元也有提升。

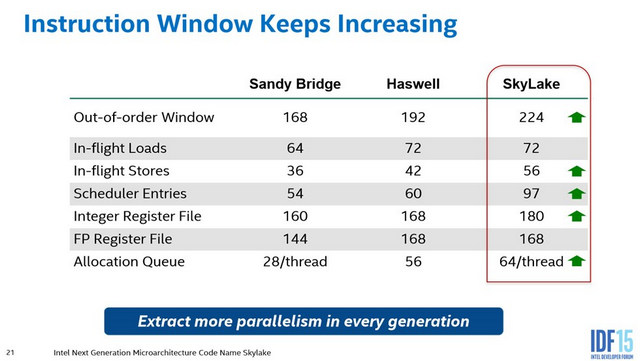

简单来说 Skylake 加宽加深了指令暂存区,除 In-Flight Loads 和 FP Register File 不变之外,In-Flight Stores 提升了 33%,Scheduler Entries 更是提升 60%以上。其它像是 AVX2 线路也可在不需要时关闭,从而更加节能。

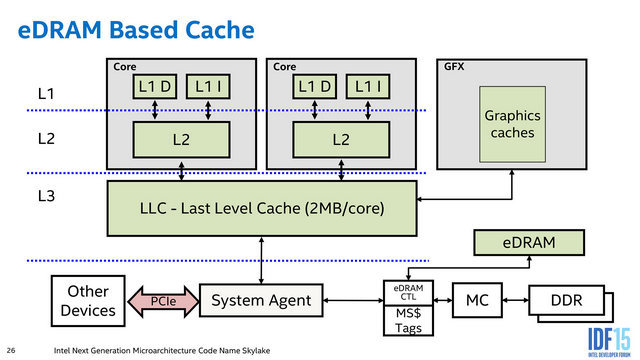

内部 Ring 汇流排负责交换资料的部分,吞吐量提升 1 倍,耗电量不变仅多了 50% 的电晶体数量,LLC(L3 快取)在处理失误时的吞吐量也提升 1 倍。此外就是 eDRAM 的变更部分,在先前的微架构中,LLC 需要有 25%(512KB)的容量花在 eDRAM 的存取标记,而且 eDRAM 也无法和处理核心、绘图核心以外的区域直接沟通。

到了 Skylake 微架构,eDRAM 的控制器接在 System Agent,能够快取处理器封装内部的所有资料,也不须再冲刷掉内部资料以维持快取一致性。改接在 System Agent 之后,对于降低耗电量也有好处,显示萤幕更新不必再唤醒部分核心。

Skylake 将 eDRAM 改由 System Agent 管理,快取一致性获得保障的同时还有降低耗电量的功用。

Intel 在 Skylake 中还加入了 Intel Speed Shift Technology,处理核心能够自行在不同的 P-State 中切换,延迟仅为 1ms。过去旧款的处理器由作业系统控制,延迟约为 30ms,不过新款的切换方式还需要作业系统协助才行(Windows 10 已支援)。

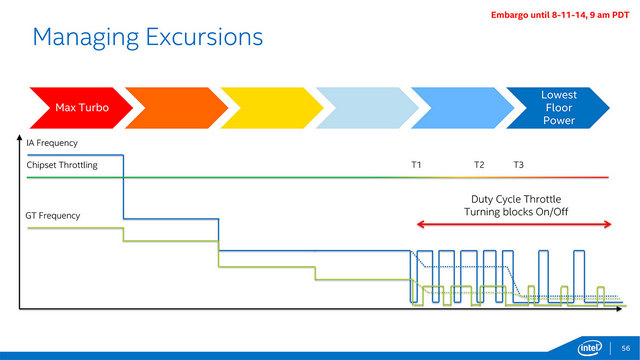

Duty Cycle Control 则是以核心的开关,模拟过去主频比较低的 P-State,直接避免晶体的漏电问题,换取更有效率的运作。SpeedStep Techonology 现在也不仅仅是支援处理核心,System Agent、DDR、eDRAM I/O 也包含在内。其它像是内部用来连接各区块的线路,也能够在工作完成时分别进入省电状态。