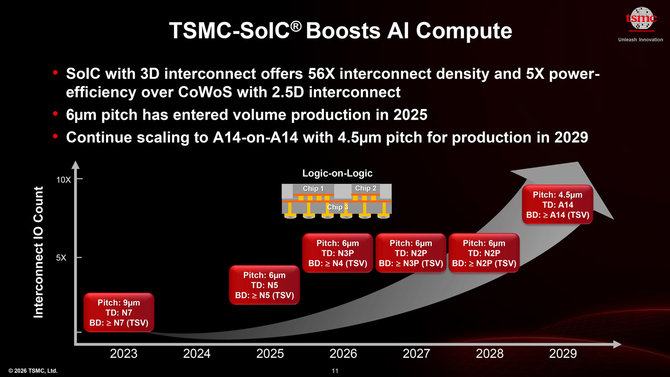

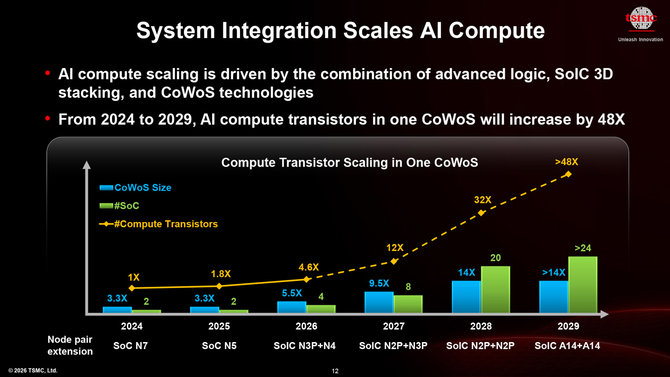

4月30日消息,台积电在北美技术研讨会上更新公布 SoIC 3D 堆叠技术路线图。台积电计划将现有 6 微米互连间距缩小,目标到 2029 年缩至 4.5 微米。SoIC 是台积电开发的 3D IC 封装技术,通过垂直堆叠多个芯片实现高性能高密度集成。

技术路径上 SoIC 分为 Face-to-Back 和 Face-to-Face 两种堆叠方式。F2B 信号密度仅 1500 个/mm2,而 F2F 通过混合铜键合技术直接连接两块芯片金属层,信号密度大幅提升至 14000 个/mm2。台积电在 2023 年实现 9 微米间距,2025 年缩短到 6 微米。

富士通 Monaka 处理器是该技术的先期重量级应用,拥有 144 个 Armv9 核心,计算模块采用 N2 工艺并通过 F2F 方式堆叠在 N5 工艺的 SRAM 芯片之上。